# Micro Engine Scheduler Specification

Date: April 2024

# **Specification Agreement**

This Specification Agreement (this "Agreement") is a legal agreement between Advanced Micro Devices, Inc. ("AMD") and "You" as the recipient of the attached AMD Specification (the "Specification"). If you are accessing the Specification as part of your performance of work for another party, you acknowledge that you have authority to bind such party to the terms and conditions of this Agreement. If you accessed the Specification by any means or otherwise use or provide Feedback (defined below) on the Specification, You agree to the terms and conditions set forth in this Agreement. If You do not agree to the terms and conditions set forth in this Agreement, you are not licensed to use the Specification; do not use, access or provide Feedback about the Specification. In consideration of Your use or access of the Specification (in whole or in part), the receipt and sufficiency of which are acknowledged, You agree as follows:

- 1. You may review the Specification only (a) as a reference to assist You in planning and designing Your product, service or technology ("Product") to interface with an AMD product in compliance with the requirements as set forth in the Specification and (b) to provide Feedback about the information disclosed in the Specification to AMD.

- 2. Except as expressly set forth in Paragraph 1, all rights in and to the Specification are retained by AMD. This Agreement does not give You any rights under any AMD patents, copyrights, trademarks or other intellectual property rights. You may not (i) duplicate any part of the Specification; (ii) remove this Agreement or any notices from the Specification, or (iii) give any part of the Specification, or assign or otherwise provide Your rights under this Agreement, to anyone else.

- 3. The Specification may contain preliminary information, errors, or inaccuracies, or may not include certain necessary information. Additionally, AMD reserves the right to discontinue or make changes to the Specification and its products at any time without notice. The Specification is provided entirely "AS IS." AMD MAKES NO WARRANTY OF ANY KIND AND DISCLAIMS ALL EXPRESS, IMPLIED AND STATUTORY WARRANTIES, INCLUDING BUT NOT LIMITED TO IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, NONINFRINGEMENT, TITLE OR THOSE WARRANTIES ARISING AS A COURSE OF DEALING OR CUSTOM OF TRADE. AMD SHALL NOT BE LIABLE FOR DIRECT, INDIRECT, CONSEQUENTIAL, SPECIAL, INCIDENTAL, PUNITIVE OR EXEMPLARY DAMAGES OF ANY KIND (INCLUDING LOSS OF BUSINESS, LOSS OF INFORMATION OR DATA, LOST PROFITS, LOSS OF CAPITAL, LOSS OF GOODWILL) REGARDLESS OF THE FORM OF ACTION WHETHER IN CONTRACT, TORT (INCLUDING NEGLIGENCE) AND STRICT PRODUCT LIABILITY OR OTHERWISE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

- 4. Furthermore, AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur.

- 5. You have no obligation to give AMD any suggestions, comments or feedback ("Feedback") relating to the Specification. However, any Feedback You voluntarily

provide may be used by AMD without restriction, fee or obligation of confidentiality. Accordingly, if You do give AMD Feedback on any version of the Specification, You agree AMD may freely use, reproduce, license, distribute, and otherwise commercialize Your Feedback in any product, as well as has the right to sublicense third parties to do the same. Further, You will not give AMD any Feedback that You may have reason to believe is (i) subject to any patent, copyright or other intellectual property claim or right of any third party; or (ii) subject to license terms which seek to require any product or intellectual property incorporating or derived from Feedback or any Product or other AMD intellectual property to be licensed to or otherwise provided to any third party.

- 6. You shall adhere to all applicable U.S., European, and other export laws, including but not limited to the U.S. Export Administration Regulations ("EAR"), (15 C.F.R. Sections 730 through 774), and E.U. Council Regulation (EC) No 428/2009 of 5 May 2009. Further, pursuant to Section 740.6 of the EAR, You hereby certifies that, except pursuant to a license granted by the United States Department of Commerce Bureau of Industry and Security or as otherwise permitted pursuant to a License Exception under the U.S. Export Administration Regulations ("EAR"), You will not (1) export, re-export or release to a national of a country in Country Groups D:1, E:1 or E:2 any restricted technology, software, or source code You receive hereunder, or (2) export to Country Groups D:1, E:1 or E:2 the direct product of such technology or software, if such foreign produced direct product is subject to national security controls as identified on the Commerce Control List (currently found in Supplement 1 to Part 774 of EAR). For the most current Country Group listings, or for additional information about the EAR or Your obligations under those regulations, please refer to the U.S. Bureau of Industry and Security's website at http://www.bis.doc.gov/.

- 7. If You are a part of the U.S. Government, then the Specification is provided with "RESTRICTED RIGHTS" as set forth in subparagraphs (c) (1) and (2) of the Commercial Computer Software-Restricted Rights clause at FAR 52.227-14 or subparagraph (c) (1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.277-7013, as applicable.

- 8. This Agreement is governed by the laws of the State of California without regard to its choice of law principles. Any dispute involving it must be brought in a court having jurisdiction of such dispute in Santa Clara County, California, and You waive any defenses and rights allowing the dispute to be litigated elsewhere. If any part of this agreement is unenforceable, it will be considered modified to the extent necessary to make it enforceable, and the remainder shall continue in effect. The failure of AMD to enforce any rights granted hereunder or to take action against You in the event of any breach hereunder shall not be deemed a waiver by AMD as to subsequent enforcement of rights or subsequent actions in the event of future breaches. This Agreement is the entire agreement between You and AMD concerning the Specification; it may be changed only by a written document signed by both You and an authorized representative of AMD.

# Contents

| MICRO ENGINE SCHEDULER SPECIFICATION     | 1  |

|------------------------------------------|----|

| SPECIFICATION AGREEMENT                  | 2  |

| Scheduling requirements                  | 5  |

| HW ARCHITECTURE OVERVIEW                 | 6  |

| Scheduler FW architecture                |    |

| Scheduling Algorithm                     |    |

| Queue state transitions                  |    |

| Round robin scheduling                   |    |

| Queue prioritization                     |    |

| MES API                                  |    |

| MES API format                           |    |

| MES_SCH_API_SET_HW_RSRC                  |    |

| MES_SCH_API_ADD_QUEUE                    |    |

| MES_SCH_API_AMD_LOG                      |    |

| MES_SCH_API_REMOVE_QUEUE                 |    |

| MES_SCH_API_SET_SCHEDULING_CONFIG        |    |

| MES_SCH_API_PERFORM_YIELD                |    |

| MES_SCH_API_SET_GANG_PRIORITY_LEVEL      |    |

| MES_SCH_API_SUSPEND                      |    |

| MES_SCH_API_RESUME                       |    |

| MES_SCH_API_RESET                        |    |

| MES_SCH_API_SET_LOG_BUFFER               |    |

| MES_SCH_API_CHANGE_GANG_PRORITY          |    |

| MES_SCH_API_QUERY_SCHEDULER_STATUS       |    |

| MES_API_QUERY_MESGET_CTX_ARRAY_SIZE      |    |

| MES_API_QUERY_MESHEALTHY_CHECK           |    |

| MES_SCH_API_PROGRAM_GDS                  |    |

| MES_SCH_API_SET_DEBUG_VMID               |    |

| MES_SCH_API_UPDATE_ROOT_PAGE_TABLE       |    |

| MES_SCH_API_SET_SE_MODE                  |    |

| MES_SCH_API_SET_GANG_SUBMIT              |    |

| MES_SCH_API_MISC                         |    |

| MESAPI_MISCWRITE_REG                     |    |

| MESAPI_MISCINV_GART                      |    |

| MESAPI_MISCQUERY_STATUS                  |    |

| MESAPI_MISCREAD_REG                      |    |

| MESAPI_MISCWAIT_REG_MEM                  |    |

| MESAPI_MISCSET_SHADER_DEBUGGER           |    |

| MESAPI_MISCNOTIFY_WORK_ON_UNMAPPED_QUEUE |    |

| MESAPI_MISCNOTIFY_TO_UNMAP_PROCESSES     |    |

| Scheduler log                            |    |

| API history                              |    |

| Event log history                        |    |

| Interrupt history                        |    |

| Example of log usage                     |    |

| DISCLAIMER                               |    |

| Notices                                  | 53 |

| TRADEMARKS                               | 54 |

# Scheduling requirements

At a high-level, the scheduling requirements can be summarized as:

- Fair and efficient scheduling of the application's work on the GPU

- Implementation of multiple priority levels for a variety of user scenarios

These high-level requirements can also be described from a user scenario perspective:

- Applications with the same priority level should get the equal amount of the GPU execution time

- Applications with the user focus (for e.g. compositor) should receive larger GPU time, but not infinitely starve the Normal priority level

- Real time work such VR, Super-Wet ink or True audio should run immediately and can infinitely starve work in the lower priority levels

- Low-priority work such as OneDrive, photo enhancement, compression or Folding@home should only run when all higher priority levels are idle

| Level     | Scheduling expectation                                                     | What runs here                                                                                      |

|-----------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Real time | Real time Lowest possible launch latency. VR compositor, Su<br>audio next. |                                                                                                     |

| Focus     | Provides no forward progress guarantee for the lower levels.               | Desktop compositor, Video post processing, foreground app's work.                                   |

| Normal    | Gets majority of GPU execution time in the absence of Real time work.      | Typical work from the application that does not have the user focus                                 |

| Low       | Ensures forward progress for the Normal level work.                        | All background work with no strict deadline requirements for e.g. file compression, encryption etc. |

Scheduler implements the above stated requirements via 4 levels of queue prioritization.

This scheduling behavior mirrors Microsoft specifications for GPU scheduling. The requirements are captured in the Microsoft GPU scheduling specification and are not explained further.

# HW architecture overview

The scheduler firmware's main role is to map the scheduling requirement on to the HW architecture. Therefore, it is required to understand the HW architecture to understand how scheduling firmware achieves the scheduling requirements on the AMD GPUs.

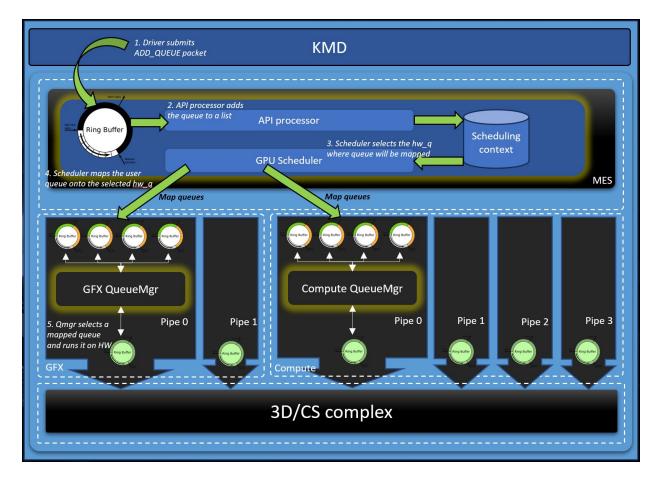

The following diagram describes the high-level HW architecture and execution flow to schedule/run an application queue.

Key highlights of HW architecture can be summarized as follows.

- The GPU frontend has three micro-processors meant to execute scheduling, compute and gfx firmware

- There are multiple GFX and Compute pipes where each pipe contains a queue mgr that arbitrates a certain number of HW queues attached to that pipe

- There are two levels of scheduling:

- First level of scheduling is at firmware, where firmware decides the applications queues that should be mapped onto the available hardware queues on various pipes

- Second level of scheduling is in the Queue Manager HW where it selects one of the ready hardware queue and runs it on the shader complex. Although the second level of scheduling is done by Queue manager hardware, scheduler FW is able to influence the Queue manager's hardware queue selection and execution via various knobs such as hardware queue priority, quantum etc.

- Queue manager's arbitration logic selects a HW queue and runs it on the shader complex. The mapped hardware queue selected for execution is called a "connected queue"

- Each pipe provides an independent path to launch a queue's work inside 3D/CS complex. So potentially there could be #pipes worth of "connected queues" running in parallel

- There is a shared pool of ALUs for GFX and compute work

Refer to <u>RDNA3 Instruction Set Architecture Reference Guide</u> for additional information.

# Scheduler FW architecture

The scheduler firmware architecture can be decomposed into following key components:

#### 1. Scheduler APIs

These are the commands sent by the driver to inform scheduler of the events such as queue creation, destruction, suspension, or any changes to its priority. Each API is described later under APIs section.

#### 2. Scheduler context

Data structures where scheduler maintains application, queue state or any other scheduling state or configuration.

Scheduler context is the state that API processor and Core scheduler thread works on. The scheduler context consists of:

#### HW resource state

- HQD State Current Queue mapped, queue type, scheduled time.

- VMID State Current process mapped

- GDS State Current process using the GDS partition.

#### Process scheduling state

- Scheduling level state process list, grace period, normalband percentage, has\_ready\_queues

- Process state Gang list for each context priority(-7/+7), processquantum, running time carryover

- Per Gang state Queuelist, running time carryover, gang quantum.

#### 3. API processor

Processes the APIs submitted by the driver and modifies the scheduler state if required.

#### 4. Core Scheduler

Looks at the scheduler state, decide next set of scheduling actions and applies them. For example, mapping a queue when it is created, or suspending as required. The scheduling algorithm is described in a dedicated section later in this document.

#### 5. Interrupt Handler

Handles interrupts from various internal HW blocks. For example, interrupt handlers reads the API data from the fetcher or collects the busy, idle state of various hardware queues. These are the main types of interrupts that RS64 processer will receive:

| Interrupt<br>source              | Description                          |

|----------------------------------|--------------------------------------|

| ME0 Pipe0                        | Gfx pipe                             |

| ME1 Pipe0/1/2/3                  | First 4 compute pipes                |

| ME2 Pipe0/1/2/3                  | Other 4 compute pipes                |

| MES packet fifo                  | Indicates new data in the MES queues |

| Hardware queue Message interrupt | QueueManager interrupts              |

| Software interrupt               | Caused by MES fw itself              |

| Timer interrupt                  | Used for Timer expiration            |

| Unprivileged access              | Unprivileged access of MES registers |

| External interrupt               | From Non-gfx blocks                  |

# Scheduling algorithm

Here are queue terminologies with descriptions to assist in understanding the queue state transitions, before describing the scheduling algorithm.

#### • User queue

Represents a linear command stream of draws or dispatches from an application. It would be analogous to a thread in the CPU world. There we few memory resources allocated for user queue such as ring buffer where command packets are submitted by the application and a memory to save the HW execution state of the queue when it is preempted. A user queue does not execute on its own. It needs to be mapped onto a HW queue for it to execute.

#### • Hardware queue

A hardware descriptor that holds the user queue state (for e.g. ring buffer address, read, write pointers etc). A hardware queue could be in a mapped or unmapped state. And a mapped queue could be in a connected or a disconnected state.

#### • Queue mapping/un-mapping

Mapping is an act of loading a user queue state onto a hardware queue. And un mapping is an act of moving the queue state from a hardware queue descriptor to memory. A hardware queue can only be unmapped after preemption.

#### Connected queue

Hardware queue that is selected by queue manager to run on the 3d/CS complex.

## Queue state transitions

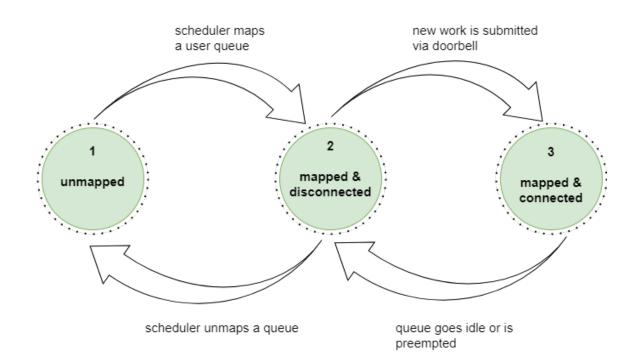

This diagram describes the possible queue states and triggers for the transitions.

### Queue State Transitions

Based on this illustration, a queue could be in one of the following states:

#### • Unmapped

The user queue has not been initialized into a hardware queue and it solely exists in memory.

#### • Mapped & disconnected

The user queue has been initialized into a hardware queue but is currently not connected to the shader subsystem so is not able to execute.

#### • Mapped and connected

The user queue has been initialized into a hardware queue and is connected to the shader subsystem. Only connected queues are able to request and launch their work on the shader resources. Only queues with pending work are allowed to connect.

The GPUSCH implementation can be explained in two steps where first we go into the round robin scheduling and secondly we look at how different levels of queue priority are implemented.

## Round robin scheduling

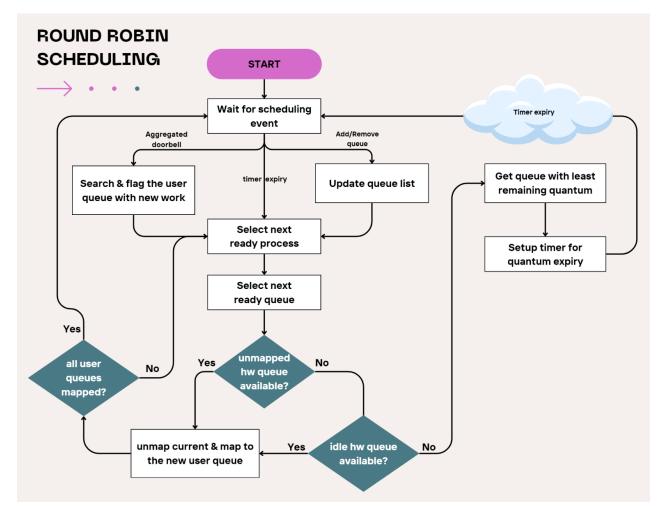

Round robin scheduling refers to the vanilla round robin scheduling where queues from all applications have the same priority, and the scheduler is expected to provide an equal amount of gpu time to each application.

Schedules achieves this by:

- maintaining a database of queues from all applications

- mapping them on to available hardware queues based on their scheduling turn. The database referred above is the scheduling context that contains queue list for each unique pair of queue type(GFX, Compute, DMA) and priority level.

There are 12 queue lists in total maintained inside the scheduler context.

Scheduler context also contains queue or process specific information such as MQD pointers, VMIDs or any special resources allocated to the queue or the process. Various APIs from the driver result in queue and process information to be updated inside the scheduler context.

Any updates to the scheduler context are then acted upon by the scheduler by performing certain scheduling actions such as queue map or unmap.

AMD GPU has certain number of pipes, and each pipe has a fixed set of hardware queues. The user queues must be mapped onto the hardware queues to execute their work. Since there are limited number of hardware queues, the scheduler will attempt to map as many user queues on the hardware queues as possible.

When a user queue is mapped on the hardware queue, the scheduler configures a quantum that the queue must run. Once the quantum has expired, the queue manager will connect the next hardware queue on the same pipe.

When the hardware queues are not over-subscribed (#user queues <= #hardware queues), the scheduler will map all user queues on the hardware queues and configure equal quantum for all queues.

This allows the queue manager to "connect" each hardware queue for an equal amount of configure time. It is possible that a "connected queue" may go idle before its quantum has expired, in which case the queue manager will connect the next hardware queue that has ready work to execute.

When the hardware queues are over-subscribed (#user queues > #hardware queues), the scheduler will map as many queues possible on the available HW queues and will unmap them gradually upon quantum expiry or when they go idle to map the queues from the next process.

To ensure that the limited number of hardware queues are used in best way possible, the scheduler only maps user queues with outstanding work to execute. This requires the scheduler

to be informed when an unmapped queue has new work.

This is achieved using aggregated doorbells. Aggregated doorbells are special doorbells that are written by SW when it submits work to an unmapped queue. Write to an aggregated doorbell informs the scheduler of new work to an unmapped queue. The scheduler then uses this notification to map the queue as soon as possible, based on the queue's priority relative to the other work. When aggregated doorbells are not available or used by the SW, scheduler start to periodically polls the write pointer memory of the unmapped queues to discover if they have new work. This is only done when there is a queue-over subscription as all user queues could not be mapped on to the limited hardware queues.

This flowchart shows the event driven scheduling design and how scheduler handles these events to implement a basic round robin scheduling of the user queues.

### Queue prioritization

The scheduler maps as many user queues as possible to the available HW queues. Once the HW queues are over-subscribed, the scheduler starts to round robin the user queues onto the available HW queues.

This basic round robin scheme falls short when it comes to executing work of varying priority

levels. The scheduler uses a combination of various hardware prioritization features to implement the desired scheduling behavior for each priority level.

Before discussing the scheduler's usage of these prioritization features, it's useful to discuss the various hardware prioritization features available for scheduler's use:

#### • Mid command buffer preemption

Queue preemption is the most fundamental feature that is employed in various prioritization scenarios to achieve the desired quality of service. Preemption can be issued at several different work boundaries that affects the latency and the amount of state that gets saved or restored. For example, compute work can be preempted at a submission, dispatch, thread group or at a shader instruction boundary. The preemption latency and amount of saved or restored states will vary based on the preemption granularity.

#### • Wave limiting

This method reduces the workload from other queues by limiting the number of waves that can be issued. "Wave" represents a group of shader threads.

#### • Pipe priority

Connected queues on each pipe asserts a pipe priority to the shader HW. The shader HW uses this priority to select and launch upcoming work based on pipe priority.

#### • Dispatch tunneling

The method immediately disables the work from other queues when a dispatch from a high-priority queue is executed. The ability to tunnel dispatches is configured as a queue-property.

#### Queue quantum

Quantum is implemented by both queue manager hardware and scheduler firmware. The queue manager connects and disconnects queues based on the quantum configured in the hardware queue by the scheduler firmware.

During queue oversubscription, the scheduler firmware un-maps the queue once its quantum has expired to allow mapping of other unmapped user queues on the hardware queues.

#### • Queue connection priority

The queue connection priority is specified for each hardware queue and is used by the queue manager hardware to select the next hardware queue that will be connected to the pipe.

#### • Compute unit reservation

This method allows a certain number of compute units to be carved out and only made available for a particular queue. This method is used in scenarios where the machine utilization launch latency is critical.

The scheduler uses a combination of the described methods to achieve the desired prioritization in the presence of workload from queues with different priorities.

The following table lists how various methods are employed in different scenarios:

| Ready work to run                                                                                                                                | Expected scheduling behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | How scheduler achieves it                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ol> <li>Real time compute<br/>queue</li> <li>Focus gfx queue</li> <li>Normal priority<br/>compute queues</li> <li>Idle Compute queue</li> </ol> | <ol> <li><i>Real time</i> priority queue<br/>runs without any delays</li> <li>Once <i>Real time</i> queue is<br/>idle, <i>Focus</i> queue will start<br/>to execute.</li> <li>Once <i>Focus</i> queue has<br/>executed for a configured<br/>amount of time, the Normal<br/>queue will execute for a<br/>certain period of time.</li> <li>Once all <i>Real time</i>, <i>Focus</i><br/>and <i>Normal</i> queues have<br/>nothing else to execute,<br/>only then the Idle queue will<br/>execute</li> </ol> | <ul> <li>Real time prioritization <ol> <li>Real time queue once created stays mapped(max 4 RT queues allowed i.e. max 1 RT queue/pipe)</li> <li>A certain # of Compute units are reserved for the Real time queue. Certain Real time queues will use Wave limiting instead of Compute unit reservation to quickly get their work to execute.</li> <li>Highest queue connection priority</li> <li>Highest shader type priority</li> </ol> </li> <li>Focus and Normal prioritization <ol> <li>Focus queue is mapped as the same connection priority as Normal queue.</li> <li>Focus queue has a larger quantum relative to the Normal queue.</li> <li>Focus queues have higher pipe priority.</li> </ol> </li> <li>Scheduler firmware may also unmap Normal queues on other pipes when they have long running shaders that prevent the Focus work from being able to launch on the compute units.</li> <li>Normal queues get preempted with a higher level of preemption than the Focus queues.</li> </ul> |

# **MES API**

This section describes MES API usage. The kernel mode driver (KMD) communicates with the Micro Engine Scheduler (MES) firmware by submitting API commands to the MES queue ring buffer.

• Some API's fields are for debug purposes which are not enabled by default. These fields have **Debug Only** in their descriptions

### **MES API format**

- MES scheduler APIs are defined in mes\_api\_def.h

- Each API has length 64 DWORDS as defined in enum {API\_FRAME\_SIZE\_IN\_DWORDS = 64}

The following format is applicable to all APIs:

```

union MESAPI__APINAME

{

struct

{

union MES_API_HEADER header;

//API specific info

struct MES_API_STATUS api_status;

uint64_t timestamp;

};

uint32_t max_dwords_in_api[API_FRAME_SIZE_IN_DWORDS];

};

```

Each API contains its specific information and three common fields: header, timestamp and api\_status:

union MES API HEADER

```

{

struct

{

uint32_t type : 4;    /* 0 - Invalid; 1 - Scheduling; 2-15 - Reserved*/

uint32_t opcode : 8;    /* API command defined in MES_SCH_API_OPCODE enum */

uint32_t dwsize : 8;    /* Size in DWORD of the API command including header */

uint32_t reserved : 12;

};

uint32_t u32All;

};

```

#### Opcode defines all supported MES APIs:

```

enum MES SCH API OPCODE

{

MES\_SCH\_API\_SET\_HW\_RSRC = 0,

MES_SCH_API_SET_SCHEDULING_CONFIG = 1,

MES SCH API ADD QUEUE = 2,

MES SCH API REMOVE QUEUE = 3,

MES SCH API PERFORM YIELD = 4,

MES SCH API SET GANG PRIORITY LEVEL = 5,

MES\_SCH\_API\_SUSPEND = 6,

MES SCH API RESUME = 7,

MES SCH API RESET = 8,

MES_SCH_API_SET_LOG_BUFFER = 9,

MES SCH API CHANGE GANG PRORITY = 10,

MES_SCH_API_QUERY_SCHEDULER_STATUS = 11,

MES_SCH_API_PROGRAM_GDS = 12,

MES SCH API SET DEBUG VMID = 13,

MES\_SCH\_API\_MISC = 14,

MES_SCH_API_UPDATE_ROOT_PAGE_TABLE = 15,

MES SCH API AMD LOG = 16,

MES\_SCH\_API\_SET\_SE\_MODE = 17,

MES SCH API SET GANG SUBMIT = 18,

MES\_SCH\_API\_MAX = OxFF

};

```

The api\_status in each API command contains fence address and fence value that the KMD inserts. MES firmware writes the fence value to the given address to notify the KMD that the API has been processed by scheduler.

```

struct MES_API_STATUS

{

uint64_t api_completion_fence_addr;

uint64_t api_completion_fence_value;

};

```

## MES\_SCH\_API\_SET\_HW\_RSRC

This is the first API that KMD submits to MES during initialization.

It provides list of hardware resources (hardware queues, virtual memory ID (VMID), etc.) to be managed by the scheduler and configuration flags (OS dependent features, workaround, etc.).

```

enum { MAX_COMPUTE_PIPES = 8 };

enum { MAX GFX PIPES = 2 };

enum { MAX SDMA PIPES = 2 };

enum MES AMD PRIORITY LEVEL

AMD PRIORITY LEVEL LOW

= 0,

AMD_PRIORITY_LEVEL_NORMAL

= 1,

AMD PRIORITY LEVEL MEDIUM

= 2,

AMD PRIORITY LEVEL HIGH

= 3,

AMD PRIORITY LEVEL REALTIME = 4,

AMD_PRIORITY_NUM_LEVELS

};

union MESAPI SET HW RESOURCES

struct

{

union MES API HEADER header;

uint32_t

vmid_mask_mmhub;

uint32 t

vmid mask gfxhub;

uint32 t

gds size;

uint32 t

paging_vmid;

uint32 t

compute_hqd_mask[MAX_COMPUTE_PIPES];

uint32 t

gfx hqd mask[MAX GFX PIPES];

uint32 t

sdma hqd mask[MAX SDMA PIPES];

uint32 t

aggregated doorbells[AMD PRIORITY NUM LEVELS];

uint64 t

g_sch_ctx_gpu_mc_ptr;

uint64_t

query_status_fence_gpu_mc_ptr;

uint32 t

gc base[MES MAX HWIP SEGMENT];

```

```

uint32 t

mmhub base[MES MAX HWIP SEGMENT];

uint32 t

osssys base[MES MAX HWIP SEGMENT];

struct MES API STATUS api status;

union

{

struct

{

uint32 t disable reset : 1;

uint32 t use different vmid compute : 1;

uint32 t disable mes log : 1;

uint32 t apply mmhub pgvm invalidate ack loss wa : 1;

uint32_t apply_grbm_remote_register_dummy_read_wa : 1;

uint32 t second gfx pipe enabled : 1;

uint32_t enable_level_process_quantum_check : 1;

uint32_t legacy_sch_mode : 1;

uint32 t disable add queue wptr mc addr : 1;

uint32_t enable_mes_event_int_logging : 1;

uint32_t enable_reg_active_poll : 1;

uint32 t use disable queue in legacy uq preemption : 1;

uint32 t send write data : 1;

uint32 t os tdr timeout override : 1;

uint32_t use_rs64mem_for_proc_gang_ctx : 1;

uint32 t use add queue unmap flag addr : 1;

uint32 t enable mes sch stb log : 1;

uint32 t reserved : 15;

};

uint32_t uint32_all;

};

uint32 t

oversubscription timer;

uint64 t

doorbell info;

uint64 t

event_intr_history_gpu_mc_ptr;

uint64 t

timestamp;

uint32 t

os tdr timeout in sec;

};

uint32 t max dwords in api[API FRAME SIZE IN DWORDS];

```

vmid\_mask\_gfxhub – Bit mask of VMIDs in GC hub that are available for scheduler to manage. Each bit position indicates the availability of the corresponding VMID, e.g., 0x6

};

means VMID 1 and 2 are available

- vmid\_mask\_mmhub Obsolete

- gds\_size Size of the global data storage (GDS) on the chip

- paging\_vmid VMID that driver assigns to paging process (excluded from vmid\_mask\_gfxhub)

- compute\_hqd\_mask Per pipe bit mask of compute hardware queue descriptors (HQD) that are managed by scheduler. Each bit position indicates the availability of corresponding compute HQD on the particular pipe, e.g., 0x3 means compute HQD 0 and 1 of the pipe are available

- gfx\_hqd\_mask Per pipe bit mask of graphics (GFX) HQDs that are managed by scheduler. Each bit position indicates the availability of corresponding GFX HQD on the particular pipe, e.g., 0x3 means GFX queue 0 and 1 of the pipe are available

- sdma\_hqd\_mask Per pipe bit mask of SDMA HQDs that are managed by scheduler.

Each bit position indicates the availability of corresponding SDMA HQD on the particular pipe, e.g., 0x3 means SDMA queue 0 and 1 of the pipe are available

- aggregated\_doorbells Offsets of aggregated doorbells. Value of OXFFFFFFF indicates invalid offset

- g\_sch\_ctx\_gpu\_mc\_ptr Obsolete

- query\_status\_fence\_gpu\_mc\_ptr MC address of query\_status packet fence memory.

- gc\_base HWIP base for GC block

- mmhub\_base HWIP base for MM block

- ossys\_base HWIP base for OSSYS block

- oversubscription\_timer Duration in micro-second of timer when oversubscription happens. Scheduler wakes up to check if any unmapped queue has new work when timer is up

- doorbell\_info Debug only. Memory to hold aggregated doorbell counter

- event\_intr\_history\_gpu\_mc\_ptr Debug only. MC address to hold MES event/interrupt/API history log

- os\_tdr\_timeout\_in\_sec Unmap timeout value in seconds. The driver is able to use this to overwrite the default unmap time out value of 2 seconds. Only valid when os\_tdr\_timeout\_override is set

### Flags

- disable\_reset Disable MES automatic hang detection

- use\_different\_vmid\_compute Scheduler assigns different VMIDs for GFX and compute of the same process

- disable\_mes\_log- Disables MSFT GPU hardware scheduling log

- apply\_mmhub\_pgvm\_invalidate\_ack\_loss\_wa Obsolete

- apply\_grbm\_remote\_register\_dummy\_read\_wa Obsolete

- second\_gfx\_pipe\_enabled Enables 2nd GFX pipe

- enable\_level\_process\_quantum\_check Enable an optimization that jumps out of the scheduling loop to handle an API event

- legacy\_sch\_mode Set to 1 on the older OSes that do not understand or support the GPU hardware scheduling.

- disable\_add\_queue\_wptr\_mc\_addr If set to 1, the scheduler uses part of memory queue descriptor (MQD) memory for wptr poll memory. Otherwise, scheduler use the address passed in ADD\_QUEUE API (see MES\_SCH\_API\_ADD\_QUEUE for details)

- enable\_mes\_event\_int\_logging Debug only. Enables MES internal event/interrupt/API logging

- enable\_reg\_active\_poll Controls how the scheduler polls queue's active bit. 1: poll HQD register; 0: poll MQD memory

- use\_disable\_queue\_in\_legacy\_uq\_preemption Set to 1 to allow the scheduler to use disable\_queue bit in MQD for OS preemption

- send\_write\_data Set to 1 for the scheduler to send a write\_date packet to write a fence following each KIQ packet

- os\_tdr\_timeout\_override Enables unmap timeout overwrite

- use\_rs64mem\_for\_proc\_gang\_ctx Enables scheduler optimization that puts the process context and gang context into the MES scheduler local memory

- use\_add\_queue\_unmap\_flag\_addr If set to 1, the scheduler uses MC address passed in MES\_SCH\_API\_ADD\_QUEUE for queue unmap status. Else, scheduler will use the MQD memory

- enable\_mes\_sch\_stb\_log Enables MES to log into Smart Trace Buffer

# MES\_SCH\_API\_ADD\_QUEUE

The KMD uses this API to add a use queue into the scheduler's internal structure to schedule it on GPU hardware.

| union M  | ESAPIADD_QUEUE                                               |                                                            |  |

|----------|--------------------------------------------------------------|------------------------------------------------------------|--|

| {        |                                                              |                                                            |  |

| str      | uct                                                          |                                                            |  |

| ł        |                                                              |                                                            |  |

|          | union MES_API_HEADER                                         | header;                                                    |  |

|          | uint32_t                                                     | process_id;                                                |  |

|          | uint64_t                                                     | <pre>page_table_base_addr;</pre>                           |  |

|          | uint64_t                                                     | process_va_start;                                          |  |

|          | uint64_t                                                     | process_va_end;                                            |  |

|          | uint64_t                                                     | process_quantum;                                           |  |

|          | uint64_t                                                     | <pre>process_context_addr;</pre>                           |  |

|          | uint64_t                                                     | gang_quantum;                                              |  |

|          | uint64_t                                                     | gang_context_addr;                                         |  |

|          | uint32_t                                                     | <pre>inprocess_gang_priority;</pre>                        |  |

|          | enum MES_AMD_PRIORITY_LEVEL                                  | <pre>gang_global_priority_level;</pre>                     |  |

|          | uint32_t                                                     | doorbell_offset;                                           |  |

|          | uint64_t                                                     | mqd_addr;                                                  |  |

| expected | uint64_t<br>d for wptr_addr                                  | <pre>wptr_addr; //From MES_API_VERSION 2, mc addr is</pre> |  |

|          | uint64_t                                                     | h_context;                                                 |  |

|          | uint64_t                                                     | h_queue;                                                   |  |

|          | enum MES_QUEUE_TYPE                                          | queue_type;                                                |  |

|          | uint32_t                                                     | gds_base;                                                  |  |

|          | uint32_t                                                     | gds_size;                                                  |  |

|          | uint32_t                                                     | gws_base;                                                  |  |

|          | uint32_t                                                     | gws_size;                                                  |  |

|          | uint32_t                                                     | oa_mask;                                                   |  |

|          | uint64_t                                                     | <pre>trap_handler_addr;</pre>                              |  |

|          | uint32_t                                                     | <pre>vm_context_cntl;</pre>                                |  |

|          | struct                                                       |                                                            |  |

|          | {                                                            |                                                            |  |

|          | uint32_t paging :                                            | 1;                                                         |  |

|          | uint32_t debug_vmid : 4;                                     |                                                            |  |

|          | uint32_t program_gds : 1;<br>uint32_t is_gang_suspended : 1; |                                                            |  |

|          |                                                              |                                                            |  |

|          | uint32_t is_tmz_queue :                                      | 1;                                                         |  |

|          |                                                              |                                                            |  |

```

uint32 t map kiq utility queue : 1;

uint32 t is kfd process : 1;

uint32 t trap en : 1;

uint32_t is_aql_queue : 1;

uint32 t skip process ctx clear : 1;

uint32 t map legacy kq : 1;

uint32 t exclusively scheduled : 1;

uint32 t is long running : 1;

uint32 t is dwm queue : 1;

uint32 t is video blit queue : 1;

uint32 t reserved : 14;

};

struct MES API STATUS

api status;

uint64_t

tma_addr;

uint32 t

sch id;

uint64 t

timestamp;

uint32 t

process_context_array_index;

uint32 t

gang_context_array_index;

uint32 t

pipe id; //used for mapping legacy kernel queue

uint32 t

queue id;

uint32 t

alignment mode setting;

uint64 t

unmap flag addr; //Used for letting driver know queue

is unmapped, mc addr is expected

};

uint32 t max dwords in api[API FRAME SIZE IN DWORDS];

};

```

- process\_id Process ID that appears in the IH Cookie as pasid. The KMD assigns unique process ID to each process

- page\_table\_base\_addr Page table base address of the process, and is programmed in VM\_CONTEXTx\_PAGE\_TABLE\_BASE\_LO/HI registers

- process\_va\_start Starting VA that's covered by the process's page table. Programmed in VM\_CONTEXTx\_PAGE\_TABLE\_START\_LO/HI

- process\_va\_end End VA that's covered by the process's page table. Programmed in VM\_CONTEXTx\_PAGE\_TABLE\_END\_LO/HI

- process\_quantum Measured in 100ns units. Indicates the minimum time a process is allowed to run on the GPU

- process\_context\_addr The memory where process specific information is saved. The scheduler owns the format of content saved in this memory. The size of the process context is defined in mes\_api\_def.h

- gang\_quantum Measured in 100ns units. Indicates the minimum amount of time a gang runs on the GPU

- gang\_context\_addr memory where gang specific information is saved. Scheduler owns the format of content saved in this memory. The size of this memory is defined in the mes\_api\_def.h

- inprocess\_gang\_priority The priority number assigned to the gang relative to other gangs within the same process

- gang\_global\_priority\_level The global priority level assigned to the gang. All queues within a gang share this priority level

- doorbell\_offset The doorbell offset (DWORD offset, i.e bits[27:2]) assigned to the queue

- mqd\_addr The MC address of queue's MQD memory

- wptr\_addr If MES\_SCH\_API\_SET\_HW\_RSRC.disable\_add\_queue\_wptr\_mc\_addr is set, GPUVA of wptr poll memory. Else, it's the MC address of wptr poll memory

- h\_context OS handle of the context

- h\_queue OS handle of the queue

- queue\_type GFX/compute/SDMA

- gds\_base/size GDS base/size

- gws\_base/size GWS base/size

- oa\_mask OA mask

- trap\_handler\_addr CWSR trap handler GPU VA

- tma\_addr CWSR TMA GPU VA

- vm\_context\_cntl Programmed in VM\_CONTEXTx\_CNTL

- sch\_id The scheduler ID of the engine node belonging to the queue

- timestamp The CPU time stamp of when driver submits this packet to the ring. Used for debugging only.

- process\_context\_array\_index The index of the process context array in scheduler's

local memory; valid only when MES\_SCH\_API\_SET\_HW\_RSRC.use\_rs64mem\_for\_proc\_gang\_ctx is **True**

- gang\_context\_array\_index The index of the gang context array in scheduler's local memory; valid only when MES\_SCH\_API\_SET\_HW\_RSRC.use\_rs64mem\_for\_proc\_gang\_ctx is True

- pipe\_id Used to map a kernel queue; the Pipe ID of the kernel queue

- queue\_id Used to map a kernel queue; the Queue ID of the kernel queue

- alignment\_mode\_setting The shader alignment mode to be programmed in SH\_MEM\_CONFIG

- unmap\_flag\_addr The MC address for queue unmap status memory. Only valid when MES\_SCH\_API\_SET\_HW\_RSRC. use\_add\_queue\_unmap\_flag\_addr is set

### Flags

- paging The queue belonging to the paging process

- debug\_vmid Process requires the debug vmid (used by RGP (Radeon GFX Profiling) tool

- program\_gds Process uses GDS

- is\_gang\_suspended A queue's context in suspended state to prevent scheduling of a queue

- is\_tmz\_queue Obsolete

- map\_kiq\_utility\_queue Obsolete

- is\_kfd\_process Queue belonging to the KFD process

- trap\_en Enables trap for shader debugger

- is\_aql\_queue The AQL queue

- map\_legacy\_kq The kernel queue

- exclusively\_scheduled Supports cooperative launch

- is\_long\_running Indicates that the queue has a long running compute job

- is\_dwm\_queue Indicates that the queue belongs to the DWM process

• is\_video\_blit\_queue - Indicates the queue is a video blit queue

## MES\_SCH\_API\_AMD\_LOG

Copy MES\_SCH\_CONTEXT to AMGLOG specified memory location for TDR analysis.

```

union MESAPI AMD LOG

{

struct

{

union MES API HEADER

header;

uint64 t

p_buffer_memory;

uint64 t

p_buffer_size_used;

struct MES_API_STATUS

api status;

uint64 t

timestamp;

};

uint32_t max_dwords_in_api[API_FRAME_SIZE_IN_DWORDS];

};

```

- p\_buffer\_memory Pointer to amdlog buffer

- p\_buffer\_size\_used Not used, buffer size is equal to sizeof(struct MES\_SCH\_CONTEXT)

### MES\_SCH\_API\_REMOVE\_QUEUE

The KMD uses this API to remove a user queue from the scheduler's internal structure.

If the queue being removed is the last queue in the gang, all information related to the gang is removed from the scheduler context.

If the removed gang is the last in the process, the process information is removed from the scheduler context.

```

union MESAPI__REMOVE_QUEUE

{

struct

{

union MES_API_HEADER header;

uint32_t doorbell_offset;

uint64_t gang_context_addr;

struct

{

```

```

uint32 t reserved01

: 1;

uint32_t unmap_kiq_utility_queue : 1;

uint32 t preempt legacy gfx queue : 1;

uint32_t unmap_legacy_queue : 1;

uint32 t reserved

: 28;

};

struct MES API STATUS

api_status;

uint32 t

pipe_id;

uint32 t

queue id;

uint64 t

tf addr;

uint32 t

tf data;

enum MES_QUEUE_TYPE

queue_type;

uint64 t

timestamp;

uint32 t

gang_context_array_index;

};

uint32 t max dwords in api[API FRAME SIZE IN DWORDS];

};

```

- doorbell\_offset Doorbell offset [DWORD offset, bits [27:2]] of the queue to be removed

- gang\_context\_addr The gang's context address that maintains the info of all queues belonging to that gang

- pipe/queue\_id Used to remove a kernel queue (i.e., queues are managed by KMD); pipe ID/queue ID of the kernel queue being removed

- tf\_addr/data Trailing fence address and value for OS preemption

- queue\_type Gfx/compute/SDMA

- gang\_context\_array\_index Index of the gang context array in scheduler's local memory; valid only when MES\_SCH\_API\_SET\_HW\_RSRC.use\_rs64mem\_for\_proc\_gang\_ctx is true

### Flags

- unmap\_kiq\_utility\_queue Obsolete

- preempt\_legacy\_gfx\_queue Indicates that this is for OS preemption

- unmap\_legacy\_queue Indicates that this is for kernel queue

# MES\_SCH\_API\_SET\_SCHEDULING\_CONFIG

Corresponds to Windows DDI DxgkDdiSetProrityBands.

Sets up process quantum and other related information during bootup for each priority band. The MES scheduler uses this information for scheduling decisions.

```

union MESAPI SET SCHEDULING CONFIG

ł

struct

{

union MES API HEADER

header;

uint64 t

grace period other levels[AMD PRIORITY NUM LEVELS];

/* Default quantum for scheduling across processes within a priority band. */

uint64 t

process quantum for level[AMD PRIORITY NUM LEVELS];

/* Default grace period for processes that preempt each other within a priority

band.*/

uint64 t

process grace period same level[AMD PRIORITY NUM LEVELS];

/* For normal level this field specifies the target GPU percentage in situations

when it's starved by the high level.

Valid values are between 0 and 50, with the default being 10.*/

normal yield percent;

uint32 t

struct MES API STATUS

api status;

uint64 t

timestamp;

};

uint32 t max dwords in api[API FRAME SIZE IN DWORDS];

};

```

- grace\_period\_other\_levels Grace period when preempting another priority band for this priority band. The value for idle priority band is ignored, as it never preempts other bands

- process\_quantum\_for\_level Default quantum for scheduling across processes within a priority band

- process\_grace\_period\_same\_level Default grace period for processes that preempt each other within a priority band

- normal\_yield\_percent For normal level this field specifies the target GPU percentage in situations when it's starved by the high level. Valid values are between 0 and 50, with the default being 10

**Note**: In current fw, only relevant quantum is process\_quantum\_for\_level, other fields are not used in scheduling/

### MES\_SCH\_API\_PERFORM\_YIELD

This API is not currently supported.

## MES\_SCH\_API\_SET\_GANG\_PRIORITY\_LEVEL

This API is not currently supported.

### MES\_SCH\_API\_SUSPEND

When MES\_SCH\_API\_SET\_HW\_RSRC.legacy\_sch\_mode is set, the KMD uses this API to suspend a single queue to prevent it from being scheduled for a single engine in Windows OS preemption.

(Used in the following DDIs in Windows: DxgkDdiSuspendContext, DxgkDdiPreemptCommand.)

```

union MESAPI SUSPEND

ł

struct

{

union MES API HEADER

header;

/* false - suspend all gangs; true - specific gang */

struct

{

uint32 t

suspend all gangs : 1;

uint32 t

reserved : 31;

};

/* gang context addr is valid only if suspend all = false */

uint64 t gang context addr;

uint64 t

suspend fence addr;

uint32 t

suspend_fence_value;

struct MES API STATUS api status;

union

{

uint32 t return value; // to be removed

uint32 t sch id; //keep the old return value temporarily for

compatibility

};

uint32 t

doorbell_offset;

uint64 t

timestamp;

enum MES QUEUE TYPE

legacy uq type;

enum MES AMD PRIORITY LEVEL legacy uq priority level;

uint32 t

gang context array index;

```

```

};

uint32_t max_dwords_in_api[API_FRAME_SIZE_IN_DWORDS];

```

};

- gang\_context\_addr Gang context address for target queue to be suspended

- suspend\_fence\_addr MC address for suspend completion fence

- suspend\_fence\_value Suspend fence ID

- doorbell\_offset Doorbell offset for target queue to be suspended. Only used if no flag is set

- gang\_context\_array\_index Gang context array index for target queue to be suspended. Valid only when MES\_SCH\_API\_SET\_HW\_RSRC.use\_rs64mem\_for\_proc\_gang\_ctx is set

The following fields are only valid for Windows OS preemption.

- return\_value Obsolete

- sch\_id -Scheduler ID for target engine to be suspended

- legacy\_uq\_type Queue type for target engine to be suspended (GFX/compute/SDMA)

- legacy\_uq\_priority\_level Priority level to be suspended

### Flags

• suspend\_all\_gangs - Not currently supported

### MES\_SCH\_API\_RESUME

The KMD uses this API to resume a single queue suspended by MES\_SCH\_API\_SUSPEND, or resume scheduling after reset.

(Used in the following DDIs in Windows OS: DxgkDdiResumeContext, DxgkDdiResumeHwEngine.)

```

union MESAPI__RESUME

{

struct

{

union MES_API_HEADER header;

/* false - resume all gangs; true - specified gang */

struct

{

uint32_t resume_all_gangs : 1;

uint32_t reserved : 31;

};

```

```

/* valid only if resume_all_gangs = false */

uint64_t gang_context_addr;

struct MES_API_STATUS api_status;

uint32_t doorbell_offset;

uint64_t timestamp;

uint32_t gang_context_array_index;

};

uint32_t max_dwords_in_api[API_FRAME_SIZE_IN_DWORDS];

};

```

- gang\_context\_addr Gang context address for target queue to be resumed. Valid only if resume\_all\_gangs = 0

- gang\_context\_array\_index Gang context array index for target queue to be resumed. Valid only if resume\_all\_gangs = 0 and MES\_SCH\_API\_SET\_HW\_RSRC.use\_rs64mem\_for\_proc\_gang\_ctx = 1

### Flags

• resume\_all\_gangs - Resume all scheduling. Meant to be called after an engine reset

### MES\_SCH\_API\_RESET

In Windows, the KMD uses this API for hang detection and reset. The MES scheduler returns a list of doorbell offsets of hung queues. If the list is empty, no hangs are detected.

Used in the following Windows DDIs; DxgkDdiQueryEngineStatus, DxgkDdiResetEngine, DxgkDdiResetHwEngine

The KMD can also use this API to reset kernel queues by setting reset\_legacy\_gfx flag.

```

union MESAPI RESET

{

struct

{

union MES API HEADER

header;

struct

{

uint32 t

reset queue only : 1; // Only reset the queue given

by doorbell offset (not entire gang)

uint32 t

hang detect then reset : 1; // Hang detection first

then reset any queues that are hung

hang detect only : 1; // Only do hang detection (no

uint32 t

reset)

```

```

uint32 t

reset legacy gfx : 1; // Reset HP and LP kernel

queues not managed by MES

uint32 t

use connected queue index : 1; // Fallback to use

conneceted queue index when CP CNTX STAT method fails (gfx pipe 0)

use_connected_queue_index_p1 : 1; // For gfx pipe 1

uint32 t

uint32 t

reserved : 26;

};

uint64 t

gang context addr;

/* valid only if reset queue only = true */

uint32 t

doorbell offset;

/* valid only if hang detect then reset = true */

uint64 t

doorbell_offset_addr;

enum MES QUEUE TYPE

queue type;

//valid only if reset legacy gfx = true

uint32_t pipe_id_lp;

uint32_t queue_id_lp;

uint32_t vmid_id_lp;

uint64 t mqd mc addr lp;

uint32_t doorbell_offset_lp;

uint64_t wptr_addr_lp;

uint32 t pipe id hp;

uint32 t queue id hp;

uint32 t vmid id hp;

uint64_t mqd_mc_addr_hp;

uint32 t doorbell offset hp;

uint64_t wptr_addr_hp;

struct MES API STATUS api status;

uint32 t

active vmids;

uint64 t

timestamp;

uint32 t

gang_context_array_index;

uint32 t

connected_queue_index;

uint32 t

connected queue index p1;

};

uint32_t max_dwords_in_api[API_FRAME_SIZE_IN_DWORDS];

};

```

- gang\_context\_addr Obsolete

- doorbell\_offset Doorbell offset of the queue. Only valid when reset\_queue\_only = 1

- doorbell\_offset\_addr MC address of memory that holds doorbell offset array. MES scheduler populates this array with offsets for queues that are hung

- queue\_type Indicates which engine MES should reset/hang detect (GFX/compute/SDMA)

- active\_vmids Workaround to indicate which VMIDs are currently active for CP\_CNTX\_STAT hang detect method

- gang\_context\_array\_index Obsolete

- connected\_queue\_index Workaround to indicate which queue is currently connected on GFX Pipe 0. Valid only when use\_connected\_queue\_index = 1

- connected\_queue\_index\_p1 Workaround to indicate which queue is currently connected on GFX Pipe 1. Valid only when use\_connected\_queue\_index\_p1 = 1

The following fields are only valid when reset\_legacy\_gfx is set and are used in Windows:

- pipe\_id\_lp Pipe ID for low priority GFX Kernel queue

- queue\_id\_lp Queue ID for low priority GFX Kernel queue

- vmid\_id\_lp VMID for low priority GFX Kernel queue

- mqd\_mc\_addr\_lp MQD MC address for low priority GFX Kernel queue

- doorbell\_offset\_lp Doorbell offset for low priority GFX Kernel queue

- wptr\_addr\_lp Write pointer poll memory address for low priority GFX Kernel queue

- pipe\_id\_hp Pipe ID for high priority GFX Kernel queue

- queue\_id\_hp Queue ID for high priority GFX Kernel queue

- vmid\_id\_hp VMID for high priority GFX Kernel queue

- mqd\_mc\_addr\_hp MQD MC address for high priority GFX Kernel queue

- doorbell\_offset\_hp Doorbell offset for high priority GFX Kernel queue

- wptr\_addr\_hp Write pointer poll memory address for high priority GFX Kernel queue

### Flags

- reset\_queue\_only Reset single queue with no hang detection

- hang\_detect\_then\_reset Performs hang detection, and reset all hung queues. Return doorbell offsets of all hung queues

- hang\_detect\_only Perform hang detection only. Returns doorbell offsets of all hung queues

- reset\_legacy\_gfx Resets legacy GFX queue

- No flag set Obsolete. The driver is expected to set one of the above flags

## MES\_SCH\_API\_SET\_LOG\_BUFFER

The KMD uses this API to save log buffer information passed from Windows OS DDI DxgkDdiSetSchedulingLogBuffer.

```

union MESAPI SET LOGGING BUFFER

ł

struct

{

union MES API HEADER

header;

/* There are separate log buffers for each queue type */

enum MES_QUEUE_TYPE

log_type;

/* Log buffer GPU Address */

uint64 t

logging buffer addr;

/* number of entries in the log buffer */

uint32 t

number of entries;

/* Entry index at which CPU interrupt needs to be signalled */

uint32 t

interrupt entry;

struct MES API STATUS

api status;

uint64 t

timestamp;

uint32 t

vmid;

};

uint32_t max_dwords_in_api[API_FRAME_SIZE_IN_DWORDS];

};

```

- log\_type Target engine type for this log buffer update (each engine has its own log buffer)

- logging\_buffer\_addr GPU virtual address of log buffer

- number\_of\_entries Log buffer size

- interrupt\_entry When number of entries logged in the log buffer reaches this log entry index, it raises an interrupt to KMD/OS. The interrupt is meant to give OS advanced warning of when the existing log buffer is going to be filled up so that it can allocate a new log buffer

## MES\_SCH\_API\_CHANGE\_GANG\_PRORITY

In the Windows use-case, this API corresponds to DDI DxgkDDiSetContextSchedulingProperties. The Windows OS changes user queue quantum to reflect changes in the owning process's status. For example, when a user's mouse focus changes from one process to another.

```

union MESAPI CHANGE GANG PRIORITY LEVEL

{

struct

{

union MES API HEADER

header;

inprocess_gang_priority;

uint32 t

enum MES AMD PRIORITY LEVEL gang global priority level;

uint64 t

gang_quantum;

uint64 t

gang_context_addr;

struct MES API STATUS

api status;

uint32 t

doorbell offset;

uint64 t

timestamp;

uint32 t

gang context array index;

struct

{

uint32 t

queue quantum scale : 2;

uint32 t

queue quantum duration : 8;

uint32 t

apply_quantum_all_processes : 1;

uint32 t

reserved

: 21;

};

};

uint32_t max_dwords_in_api[API_FRAME_SIZE_IN_DWORDS];

};

```

- inprocess\_gang\_priority Gang priority within a process, not used in current FW

- gang\_global\_priority\_level Overall gang priority level, lower priority gangs tend to get preempted for high priority gangs during scheduling

- gang\_quantum Quantum provided by Windows OS, usually 2ms, queue is considered "expired" after its quantum runs out

- doorbell\_offset Obsolete

- gang\_context\_array\_index index of the gang context array in scheduler's local memory; valid only when MES\_SCH\_API\_SET\_HW\_RSRC.use\_rs64mem\_for\_proc\_gang\_ctx is set

- queue\_quantum\_scale Used by Windows OS

- queue\_quantum\_duration Used by Windows OS

- apply\_quantum\_all\_processes Used by Windows OS

# MES\_SCH\_API\_QUERY\_SCHEDULER\_STATUS

The KMD uses this API to query status/info from MES firmware.

```

enum MES_API_QUERY_MES_OPCODE

{

MES API QUERY MES GET CTX ARRAY SIZE,

MES API QUERY MES CHECK HEALTHY,

MES API QUERY MES MAX,

};

union MESAPI QUERY MES STATUS

{

struct

{

union MES API HEADER

header;

enum MES_API_QUERY_MES_OPCODE subopcode;

struct MES API STATUS

api status;

uint64 t

timestamp;

union

{

struct MES_API_QUERY_MES__CTX_ARRAY_SIZE ctx_array_size;

struct MES_API_QUERY_MES__HEALTHY_CHECK healthy_check;

uint32 t data[QUERY MES MAX SIZE IN DWORDS];

};

};

uint32 t max dwords in api[API FRAME SIZE IN DWORDS];

};

```

subopcode - Changes functionality based on what MES\_API\_QUERY\_MES\_OPCODE is used

# MES\_API\_QUERY\_MES\_\_GET\_CTX\_ARRAY\_SIZE

The KMD uses this to query MES internal structure size.

```

struct MES_API_QUERY_MES__CTX_ARRAY_SIZE

{

uint64_t proc_ctx_array_size_addr;

uint64_t gang_ctx_array_size_addr;

};

```

- proc\_ctx\_array\_size\_addr Memory address where MES will write process context array size

- gang\_ctx\_array\_size\_addr Memory address where MES will write gang context array size

## MES\_API\_QUERY\_MES\_HEALTHY\_CHECK

The KMD uses this API to check if MES is running and responding.

```

struct MES_API_QUERY_MES_HEALTHY_CHECK

{

uint64_t healthy_addr;

};

```

healthy\_addr - Not used. Currently, MES firmware writes fence to the memory to notify KMD that MES is not hang

## MES\_SCH\_API\_PROGRAM\_GDS

The KMD uses this API to request MES for GDS programming for the target process. GDS registers are programmed when VMID is allocated. If VMID is already allocated, registers will be programmed before API returns.

```

union MESAPI PROGRAM GDS

{

struct

{

union MES API HEADER

header;

uint64 t

process context addr;

uint32 t

gds base;

uint32 t

gds size;

uint32 t

gws base;

uint32 t

gws size;

uint32 t

oa_mask;

struct MES_API_STATUS

api_status;

uint64 t

timestamp;

uint32 t

process context array index;

};

uint32 t max dwords in api[API FRAME SIZE IN DWORDS];

```

};

• process\_context\_addr - Memory where process specific information is saved. Scheduler owns the format of this memory. The size of the process context is defined in the

mes\_api\_def.h

- gds\_base GDS base address. Programming for GDS\_VMIDx\_BASE register •

- gds\_size GDS aperture size. Programming for GDS\_VMIDx\_SIZE register •

- gws\_base GWS base. Programming for BASE field in GDS\_GWS\_VMIDx register •

- gws\_size GWS size. Programming for SIZE field in GDS\_GWS\_VMIDx register •

- oa\_mask Bit mask representing the alloc counters allocated VMID can use. Programming for GDS\_OA\_VMIDx register

- process\_context\_array\_index Processes context array index for target process. Valid • only when MES SCH API SET HW RSRC.use rs64mem for proc gang ctx is set

## MES\_SCH\_API\_SET\_DEBUG\_VMID

ł

The KMD uses this API to set up the page table for a process that requests debug VMID for tools like Radeon GPU Profiler (RGP).

The user mode driver can request debug VMID, and KMD/MES will allocate a VMID for this process. The page table base registers for this allocated debug VMID will be programed to this process's page table base.

```

union MESAPI SET DEBUG VMID

struct

{

union MES API HEADER

header;

struct MES_API_STATUS

api status;

union

{

struct

{

uint32 t use gds : 1;

uint32 t operation : 2;

uint32 t reserved : 29;

}flags;

uint32 t u32All;

};

uint32 t

reserved;

uint32 t

debug vmid;

uint64 t

process context addr;

uint64 t

page table base addr;

uint64 t

process_va_start;

uint64 t

process_va_end;

```

|                                                       | uint32_t            | gds_base;                                                   |

|-------------------------------------------------------|---------------------|-------------------------------------------------------------|

|                                                       | uint32_t            | gds_size;                                                   |

|                                                       | uint32_t            | gws_base;                                                   |

|                                                       | uint32_t            | gws_size;                                                   |

|                                                       | uint32_t            | oa_mask;                                                    |

| 7                                                     | uint64_t            | <pre>output_addr; // output addr of the acquired vmid</pre> |

| value                                                 |                     |                                                             |

|                                                       | uint64_t            | timestamp;                                                  |

|                                                       | uint32_t            | process_vm_cntl;                                            |

|                                                       | enum MES_QUEUE_TYPE | queue_type;                                                 |

|                                                       | uint32_t            | <pre>process_context_array_index;</pre>                     |

|                                                       | uint32_t            | alignment_mode_setting;                                     |

| };                                                    |                     |                                                             |

|                                                       |                     |                                                             |

| uint32_t max_dwords_in_api[API_FRAME_SIZE_IN_DWORDS]; |                     |                                                             |

| };                                                    |                     |                                                             |

- debug\_vmid The VMID reserved as the debug VMID, used when operation flag = DEBUG\_VMID\_OP\_RELEASE (2)

- process\_context\_addr Memory where process specific context is saved. Scheduler owns the format of this memory. The size of the process context is defined in the mes\_api.def.h, this is for the process that requests the debug VMID

- page\_table\_base\_addr page table base address of the process

- process\_va\_start Starting address of the process's VA space

- process\_va\_end Ending address of the process's VA space

- gds\_base/size GDS base/size

- gws\_base/size GWS base/size

- oa\_mask OA mask

- output\_addr MES scheduler writes the allocated debug VMID value to this address for driver to read. This is used when operation flag = DEBUG\_VMID\_OP\_ALLOCATE (1)

- process\_vm\_cntl Not used

- queue\_type gfx/compute/SDMA

- process\_context\_array\_index Index of the process context array in scheduler's local memory; valid only when MES\_SCH\_API\_SET\_HW\_RSRC.use\_rs64mem\_for\_proc\_gang\_ctx is set

- alignment\_mode\_setting alignment mode setting to be programmed in SH\_MEM\_CONFIG

## MES\_SCH\_API\_UPDATE\_ROOT\_PAGE\_TABLE

The KMD uses this API to change page table base of a process.

```

union MESAPI___UPDATE_ROOT_PAGE_TABLE

{

struct

{

union MES API HEADER header;

uint64 t

page table base addr;

uint64 t

process context addr;

struct MES API STATUS

api_status;

uint64 t

timestamp;

uint32 t

process context array index;

};

uint32_t max_dwords_in_api[API_FRAME_SIZE_IN_DWORDS];

};

```

- page\_table\_base\_addr Page table base address

- process\_context\_addr Memory where process specific context is saved

- process\_context\_array\_index Index of the process context array in scheduler's local memory; valid only when MES\_SCH\_API\_SET\_HW\_RSRC.use\_rs64mem\_for\_proc\_gang\_ctx is set

## MES\_SCH\_API\_SET\_SE\_MODE

The API allows the driver to turn off the second shader engine.

```

enum MES_SE_MODE

{

MES_SE_MODE_INVALID = 0,

MES_SE_MODE_SINGLE_SE = 1,

MES_SE_MODE_DUAL_SE = 2,

MES_SE_MODE_LOWER_POWER = 3,

};

union MESAPI__SET_SE_MODE

{

struct

{

union MES_API_HEADER header;

/* the new SE mode to apply*/

MES_SE_MODE new_se_mode;

/* the fence to make sure the ItCpgCtxtSync packet is completed */

```

```

uint64 t cpg ctxt sync fence addr;

uint32_t cpg_ctxt_sync_fence_value;

/* log_seq_time - Scheduler logs the switch seq start/end ts in the IH cookies */

union

{

struct

{

uint32 t log seq time : 1;

uint32 t reserved : 31;

};

uint32_t uint32_all;

};

struct MES_API_STATUS api_status;

};

uint32_t max_dwords_in_api[API_FRAME_SIZE_IN_DWORDS];

};

```

new\_se\_mode - New SE mode to be applied

## MES\_SCH\_API\_SET\_GANG\_SUBMIT

The KMD uses this API to pair two queues together for the purpose of gang submission. MES scheduler will guarantee that the paired queues will always be mapped at the same time.

```

struct SET_GANG_SUBMIT

{

uint64_t gang_context_addr;

uint64_t slave_gang_context_addr;

uint32_t gang_context_array_index;

uint32_t slave_gang_context_array_index;

};

union MESAPI_SET_GANG_SUBMIT

{

struct

{

union MES_API_HEADER header;

struct MES_API_STATUS api_status;

struct SET_GANG_SUBMIT set_gang_submit;

};

```

```

uint32 t max dwords in api[API FRAME SIZE IN DWORDS];

```

};

- gang\_context\_addr Gang context address of master queue •

- slave\_gang\_context\_addr Gang context address of slave queue •

- gang\_context\_array\_index Gang context array index of master queue. Valid only when • use rs64mem for proc gang ctx is set in mes sch api set hw rsrc

- slave\_gang\_context\_array\_index Gang context array index of slave queue. Valid only • when use\_rs64mem\_for\_proc\_gang\_ctx is set in mes\_sch\_api\_set\_hw\_rsrc

### MES\_SCH\_API\_MISC

ł

This API contains miscellaneous non-scheduling functionalities. Each functionality has a subopcode and corresponding structures.

```

union MESAPI MISC

struct

{

union MES_API_HEADER header;

enum MESAPI MISC OPCODE opcode;

struct MES API_STATUS api_status;

union

{

struct WRITE REG write reg;

struct INV GART inv gart;

struct QUERY STATUS query status;

struct READ REG read reg;

struct WAIT REG MEM wait reg mem;

struct SET_SHADER_DEBUGGER set_shader_debugger;

enum MES AMD PRIORITY LEVEL queue sch level;

uint32_t data[MISC_DATA_MAX_SIZE_IN_DWORDS];

};

uint64 t

timestamp;

uint32 t

doorbell offset;

uint32 t

os fence;

};

uint32 t max dwords in api[API FRAME SIZE IN DWORDS];

```

| };                                        |  |  |

|-------------------------------------------|--|--|

|                                           |  |  |

| enum MESAPI_MISC_OPCODE                   |  |  |

| {                                         |  |  |

| MESAPI_MISCWRITE_REG,                     |  |  |

| MESAPI_MISCINV_GART,                      |  |  |

| MESAPI_MISCQUERY_STATUS,                  |  |  |

| MESAPI_MISCREAD_REG,                      |  |  |

| MESAPI_MISCWAIT_REG_MEM,                  |  |  |

| MESAPI_MISCSET_SHADER_DEBUGGER,           |  |  |

| MESAPI_MISCNOTIFY_WORK_ON_UNMAPPED_QUEUE, |  |  |

| MESAPI_MISCNOTIFY_TO_UNMAP_PROCESSES,     |  |  |

|                                           |  |  |

| MESAPI_MISCMAX,                           |  |  |

| };                                        |  |  |

opcode - Changes functionality based on what MESAPI\_MISC\_OPCODE is used. See each opcode's section for more details

## MESAPI\_MISC\_WRITE\_REG

Perform register write on request of KMD.

```

struct WRITE_REG

{

uint32_t reg_offset;

uint32_t reg_value;

};

```

- reg\_offset Offset of the register

- reg\_value Value to be written to the register

## MESAPI\_MISC\_INV\_GART

#### Perform GART invalidation.

```

struct INV_GART

{

uint64_t inv_range_va_start;

uint64_t inv_range_size;

};

```

• inv\_range\_va\_start - starting VA for invalidation range

• inv\_range\_size - invalidation range size

**Note**: If inv\_range\_va\_start = 0 or inv\_range\_size = 0, then MES scheduler invalidates entire range.